# IA-64 Software Conventions and Runtime Architecture Guide

August 1999

Order Number: 245256-001

Information in this document is provided in connection with Intel products. No license, express or implied, by estoppel or otherwise, to any intellectual property rights is granted by this document. Except as provided in Intel's Terms and Conditions of Sale for such products, Intel assumes no liability whatsoever, and Intel disclaims any express or implied warranty, relating to sale and/or use of Intel products including liability or warranties relating to fitness for a particular purpose, merchantability, or infringement of any patent, copyright or other intellectual property right. Intel products are not intended for use in medical, life saving, or life sustaining applications.

Intel may make changes to specifications and product descriptions at any time, without notice.

Designers must not rely on the absence or characteristics of any features or instructions marked "reserved" or "undefined." Intel reserves these for future definition and shall have no responsibility whatsoever for conflicts or incompatibilities arising from future changes to them.

The NAME OF PRODUCT may contain design defects or errors known as errata which may cause the product to deviate from published specifications. Current characterized errata are available on request.

Contact your local Intel sales office or your distributor to obtain the latest specifications and before placing your product order.

Copies of documents which have an ordering number and are referenced in this document, or other Intel literature may be obtained by calling 1-800-548-4725 or by visiting Intel's website at http://www.intel.com.

Copyright © Intel Corporation, 1999

\*Third-party brands and names are the property of their respective owners.

| 1 | Introd                                 | luction to the IA-64 Software Conventions and Runtime Architecture Guide.                                                                                             | 1-1                      |

|---|----------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------|

|   | 1.1<br>1.2<br>1.3<br>1.4               | Objectives of the Runtime Architecture                                                                                                                                | 1-1<br>Guide 1-2         |

| 2 | IA-64                                  | Processor Architecture                                                                                                                                                | 2-1                      |

|   | 2.1<br>2.2                             | Application State and Programming ModelFloating-point Programming Model                                                                                               |                          |

| 3 | Memo                                   | ory Model                                                                                                                                                             | 3-1                      |

|   | 3.1<br>3.2<br>3.3                      | Program segments Protection areas  Data Allocation  3.3.1 Global Variables  3.3.2 Local Static Data  3.3.3 Constants and Literals  3.3.4 Local Memory Stack Variables | 3-2<br>3-4<br>3-4<br>3-4 |

| 4 | Data                                   | Representation                                                                                                                                                        | 4-1                      |

|   | 4.1<br>4.2<br>4.3<br>4.4               | Fundamental TypesAggregate TypesBit FieldsFortran Data Types                                                                                                          | 4-2<br>4-5               |

| 5 | Regis                                  | ter Usage                                                                                                                                                             | 5-1                      |

|   | 5.1<br>5.2<br>5.3<br>5.4<br>5.5<br>5.6 | Partitioning General Registers Floating-point Registers Predicate Registers Branch Registers Application Registers                                                    | 5-1<br>5-2<br>5-3        |

| 6 | Regis                                  | ter Stack                                                                                                                                                             | 6-1                      |

|   | 6.1<br>6.2<br>6.3<br>6.4<br>6.5        | Input and Local Registers Output Registers Rotating Registers Frame Markers Backing Store for Register Stack                                                          | 6-1<br>6-2<br>6-2        |

| 7 | Memo                                   | ory Stack                                                                                                                                                             | 7-1                      |

|   | 7.1                                    | Procedure Frames                                                                                                                                                      | 7-1                      |

| 8 | Proce                                  | dure Linkage                                                                                                                                                          | 8-1                      |

|   | 8.1<br>8.2<br>8.3                      | External Naming Conventions The gp Register Types of Calls                                                                                                            | 8-1                      |

|     | 8.4    | Calling Sequence                                                | 8-2   |

|-----|--------|-----------------------------------------------------------------|-------|

|     |        | 8.4.1 Direct Calls                                              | 8-2   |

|     |        | 8.4.2 Indirect Calls                                            | 8-4   |

|     | 8.5    | Parameter Passing                                               | 8-5   |

|     |        | 8.5.1 Allocation of Parameter Slots                             | 8-6   |

|     |        | 8.5.2 Register Parameters                                       | 8-7   |

|     |        | 8.5.3 Memory Stack Parameters                                   | 8-10  |

|     |        | 8.5.4 Variable Argument Lists                                   | 8-10  |

|     |        | 8.5.5 Pointers to Formal Parameters                             | 8-10  |

|     |        | 8.5.6 Languages Other than C                                    | 8-10  |

|     |        | 8.5.7 Rounding Floating-point Values                            | 8-11  |

|     |        | 8.5.8 Examples                                                  | 8-11  |

|     | 8.6    | Return Values                                                   | 8-13  |

|     | 8.7    | Requirements for Unwinding the Stack                            | 8-14  |

| 9   | Coding | g Conventions                                                   | 0_1   |

| 3   |        | _                                                               |       |

|     | 9.1    | Sample Code Sequences                                           |       |

|     |        | 9.1.1 Addressing "own" Data in the Short Data Area              |       |

|     |        | 9.1.2 Addressing External Data or Data in a Long Data Area      |       |

|     |        | 9.1.3 Addressing Literals in the Text Segment                   |       |

|     |        | 9.1.4 Materializing Function Pointers                           |       |

|     |        | 9.1.5 Direct Procedure Calls                                    |       |

|     |        | 9.1.6 Indirect Procedure Calls                                  |       |

|     |        | 9.1.7 Jump Tables                                               |       |

|     | 9.2    | Speculation                                                     |       |

|     | 9.3    | Multi-threaded Code                                             |       |

|     | 9.4    | setjmp and longjmp                                              |       |

|     | 9.5    | Up-level Referencing                                            |       |

|     | 9.6    | C++ Conventions                                                 | 9-5   |

| 10  | Conte  | xt Management                                                   | 10-1  |

|     | 10.1   | Process/thread context                                          | 10-1  |

|     | 10.2   | User-level thread switch, coroutines                            |       |

|     | 10.3   | setjmp/longjmp                                                  |       |

| 4.4 |        |                                                                 |       |

| 11  |        | Unwinding and Exception Handling                                |       |

|     | 11.1   | Unwinding the Stack                                             | 11-2  |

|     |        | 11.1.1 Initial Context                                          |       |

|     |        | 11.1.2 Step to Previous Frame                                   |       |

|     | 11.2   | Exception Handling Framework                                    |       |

|     | 11.3   | Coding Conventions for Reliable Unwinding                       |       |

|     |        | 11.3.1 Conventions for Prologue Regions                         |       |

|     |        | 11.3.2 Conventions for Body Regions                             |       |

|     |        | 11.3.3 Conventions for the Spill Area in the Memory Stack Frame | 11-7  |

|     | 11.4   | Data Structures                                                 |       |

|     |        | 11.4.1 Unwind Table                                             |       |

|     |        | 11.4.2 Unwind Descriptor Area                                   |       |

|     |        | 11.4.2.1 Region header records                                  |       |

|     |        | 11.4.2.2 Descriptor records for prologue regions                |       |

|     |        | 11.4.2.3 Rules for Using Unwind Descriptors                     |       |

|     |        | 11.4.2.4 Descriptor Records for Body Regions                    | 11-16 |

|    |        | 11.4.2.5 Processing Unwind Descriptors                      | 11-18 |

|----|--------|-------------------------------------------------------------|-------|

|    |        | 11.4.3 Language-specific data area                          | 11-18 |

| 12 | Dynan  | nic Linking                                                 | 12-1  |

|    | 12.1   | Position-Independent Code                                   | 12-1  |

|    | 12.2   | Procedure Calls and Long Branch Stubs                       | 12-1  |

|    | 12.3   | Access to the Data Segment                                  | 12-1  |

|    |        | 12.3.1 Access to Constants and Literals in the Text Segment | 12-2  |

|    |        | 12.3.2 Materializing Function Pointers                      | 12-2  |

|    | 12.4   | Import stubs                                                |       |

|    | 12.5   | The dynamic loader                                          | 12-2  |

| 13 | Syster | m Interfaces                                                | 13-1  |

|    | 13.1   | Program Startup                                             | 13-1  |

|    |        | 13.1.1 Initial Memory Stack                                 | 13-1  |

|    |        | 13.1.2 Initial Register Values                              | 13-1  |

|    | 13.2   | System Calls                                                |       |

|    | 13.3   | Traps and Signals                                           | 13-2  |

| A  | Standa | ard Header Files                                            | A-1   |

|    | A.1    | Implementation Limits                                       | A-1   |

|    | A.2    | Floating-Point Definitions                                  | A-1   |

|    | A.3    | Variable Argument List Macros                               | A-2   |

|    | A.4    | Setjmp/Longjmp                                              | A-3   |

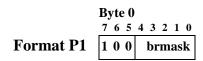

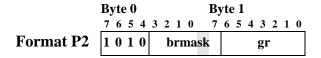

| В  | Unwin  | d Descriptor Record Format                                  | B-1   |

|    | B.1    | Overview                                                    | B-1   |

|    | B.2    | Region Header Records                                       | B-2   |

|    | B.3    | Descriptor Records for Prologue Regions                     |       |

|    | B.4    | Descriptor Records for Body Regions                         |       |

|    | B.5    | Descriptor Records for Body or Prologue Regions             | B-8   |

|    |        |                                                             |       |

# **Figures**

| 4-1  | Structure Smaller Than a Word                           | 4-2 |

|------|---------------------------------------------------------|-----|

| 4-2  | No Padding                                              |     |

| 4-3  | Internal Padding                                        |     |

| 4-4  | Internal and Tail Padding                               |     |

| 4-5  | Union Allocation                                        | 4-4 |

| 4-6  | Bit Numbering                                           | 4-5 |

| 4-7  | Bit Field Allocation                                    | 4-6 |

| 4-8  | Boundary Alignment                                      | 4-6 |

| 4-9  | Storage Unit Sharing                                    |     |

| 4-10 | Union Allocation                                        |     |

| 4-11 | Unnamed Bit Fields                                      | 4-7 |

| 6-1  | Operation of the Register Stack                         | 6-2 |

| 7-1  | Procedure frame                                         | 7-1 |

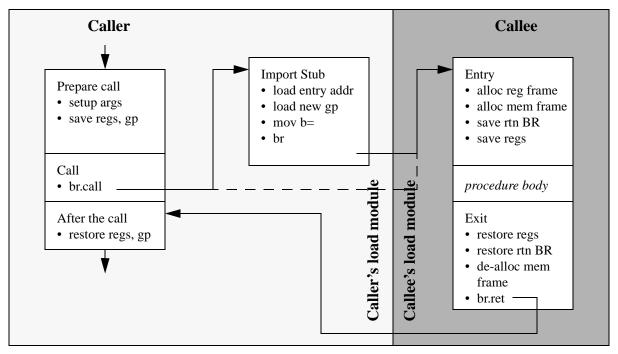

| 8-1  | Direct procedure calls                                  | 8-2 |

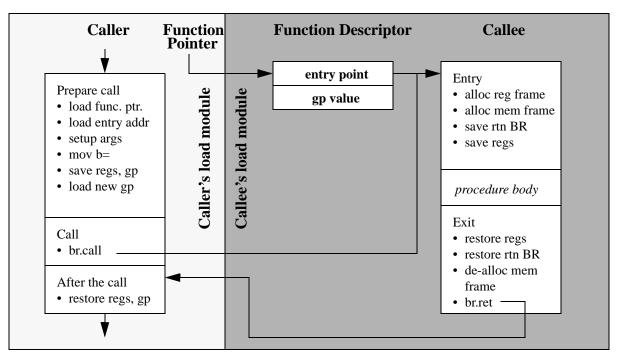

| 8-2  | Indirect Procedure Calls                                |     |

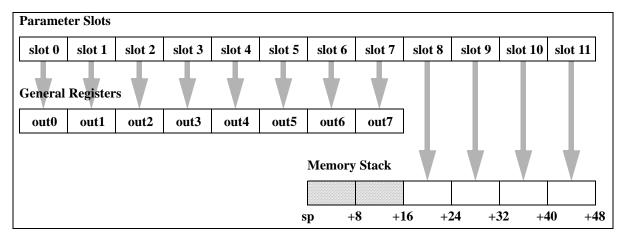

| 8-3  | Parameter Passing in General Registers and Memory       | 8-5 |

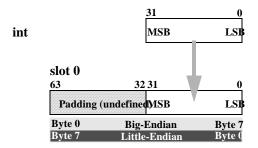

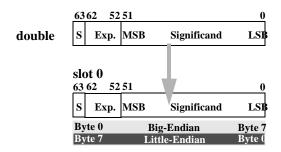

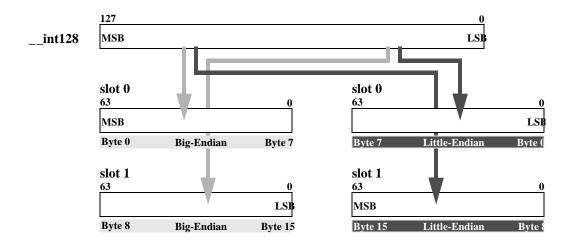

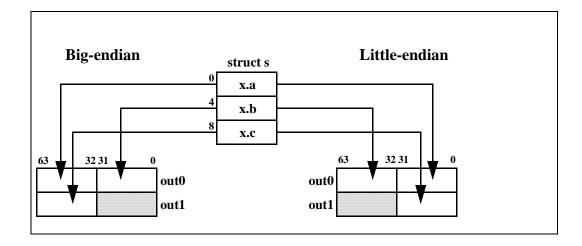

| 8-4  | Examples of "LSB" Alignment                             |     |

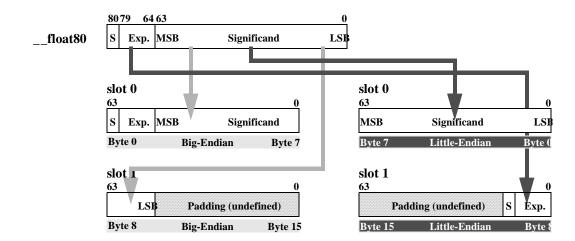

| 8-5  | Example of "Byte 0" Alignment                           | 8-9 |

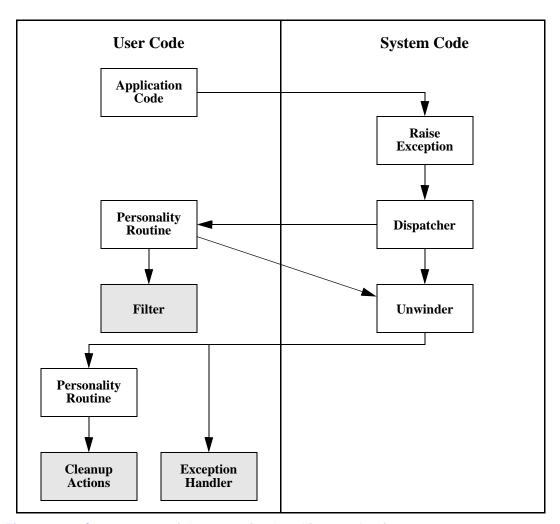

| 11-1 | Components of the exception handling mechanism          |     |

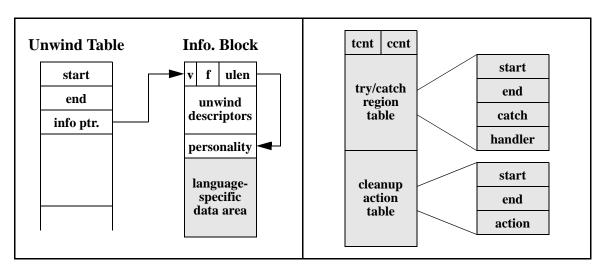

| 11-2 | Unwind table and example of language-specific data area |     |

# **Tables**

| 2-1   | Software Interrupts                                                | 2-2   |

|-------|--------------------------------------------------------------------|-------|

| 3-1   | Program Segments                                                   | 3-1   |

| 3-2   | Protection Areas                                                   | 3-2   |

| 3-3   | Alignment Requirements for Global Objects                          | 3-4   |

| 4-1   | Scalar Data types Supported by IA-64                               | 4-1   |

| 4-2   | Bit Field Base Types                                               | 4-5   |

| 4-3   | Fortran Data Types                                                 | 4-8   |

| 5-1   | General Registers                                                  | 5-1   |

| 5-2   | Floating-Point Registers                                           | 5-3   |

| 5-3   | Predicate Registers                                                | 5-3   |

| 5-4   | Branch Registers                                                   |       |

| 5-5   | Application Registers                                              | 5-4   |

| 8-1   | Rules for Allocating Parameter Slots                               | 8-6   |

| 8-2   | Rules for Return Values                                            | 8-13  |

| 10-1  | Resources to be saved on context switches                          | 10-1  |

| 11-1  | Region Header Records                                              |       |

| 11-2  | Prologue Descriptor Records for the Stack Frame                    |       |

| 11-3  | Prologue Descriptor Records for the Return Pointer                 |       |

| 11-4  | Prologue Descriptor Records for the Previous Function State        |       |

| 11-5  | Prologue Descriptor Records for Predicate Registers                |       |

| 11-6  | Prologue Descriptor Records for GRs, FRs, and BRs                  |       |

| 11-7  | Prologue Descriptor Records for the User NaT Collection Register . |       |

| 11-8  | Prologue Descriptor Records for the Loop Counter Register          |       |

| 11-9  | Prologue Descriptor Records for the Floating-Point Status Register |       |

| 11-10 | Prologue Descriptor Records for the Primary unat Collection        |       |

| 11-11 | Prologue Descriptor Records for the Backing Store                  | 11-15 |

| 11-12 | Body Region Descriptor Records                                     | 11-17 |

| 11-13 | General Unwind Descriptors                                         |       |

| 13-1  | Initial Value of the Floating-Point Status Register                | 13-1  |

| B-1   | Record Formats                                                     |       |

| B-2   | Example ULEB128 Encodings                                          | B-2   |

|       |                                                                    |       |

# intel<sub>®</sub>

# Introduction to the IA-64 Software Conventions and Runtime Architecture Guide

This document describes common 64-bit software conventions for the Intel IA-64 Architecture. It does not define operating-system interfaces or any conventions specific to any single operating system.

The runtime architecture defines most of the conventions necessary to compile, link, and execute a program on an operating system that supports these conventions. Its purpose is to ensure that object modules produced by different compilers can be linked together into a single application, and to specify the interfaces between compilers and linker, and between linker and operating system.

The runtime architecture does not specify the Application Programming Interface (API), the set of services provided by the operating system to the program, nor does it specify certain conventions that are specific to each operating system. Thus, conformance to the runtime architecture alone is not sufficient to produce a program that will execute on all IA-64 platforms. It does, however, allow many of the development tools to be shared among various operating systems.

When combined with the instruction set architecture, an API, and system-specific conventions, this runtime architecture leads to an Application Binary Interface (ABI). In other words, an ABI is the composition of an API, system-specific conventions, a hardware description, and a runtime architecture.

# 1.1 Objectives of the Runtime Architecture

This document defines the software interfaces needed to ensure that software for IA-64 will operate correctly together. The intent is to define as small a set of interface specifications as possible, while still meeting the following goals:

- Support 64-bit addressing and data types

- High performance

- Ease of porting

- Ease of interfacing with IA-32

- Ease of implementation and use

- Complete enough to insure software compatibility

### 1.2 About the Conventions

ANSI C serves as the reference programming language. By defining the implementation of C data types, the software conventions can give precise system interface information without resorting to assembly language. Giving C language bindings for system services does *not* preclude bindings for other programming languages. Moreover, the examples given here are not intended to specify any particular C language implementation available on the system.

# 1.3 Overview of the IA-64 Software Conventions and Runtime Architecture Guide

```

Chapter 1, "Introduction to the IA-64 Software Conventions and Runtime Architecture Guide".

Chapter 2, "IA-64 Processor Architecture".

Chapter 3, "Memory Model".

Chapter 4, "Data Representation".

Chapter 5, "Register Usage".

Chapter 6, "Register Stack".

Chapter 7, "Memory Stack".

Chapter 8, "Procedure Linkage".

Chapter 9, "Coding Conventions".

Chapter 10, "Context Management".

Chapter 11, "Stack Unwinding and Exception Handling".

Chapter 12, "Dynamic Linking".

Chapter 13, "System Interfaces".

Appendix A, "Standard Header Files".

Appendix B, "Unwind Descriptor Record Format".

```

# 1.4 Terminology

The following terms will be used in the rest of this document:

**Absolute address.** In this document, the term absolute address refers to a virtual address, not a physical address. It is an address within the process' address space that is computed as an absolute number, without the use of a base register.

**Binding.** The process of resolving a symbolic reference in one module by finding the definition of the symbol in another module, and substituting the address of the definition in place of the symbolic reference. The linker binds relocatable object modules together, and the DLL loader binds executable load modules. When searching for a definition, the linker and DLL loader search each module in a certain order, so that a definition of a symbol in one module has precedence over a definition of the same symbol in a later module. This order is called the **binding order**.

**Dynamic-link library (DLL).** A library that is prepared by the linker for quick loading and binding when a program is invoked, or while the program is running. A DLL is designed so that its code is shared by all processes that are bound to it. (Also called **shared library**.)

#### Introduction to the IA-64 Software Conventions and Runtime Architecture Guide

**Execution time.** The time during which a program is actually executing, not including the time during which it and its DLLs are being loaded.

**Function pointer.** A reference or pointer to a function. A function pointer takes the form of a pointer to a special descriptor (a **function descriptor**) that uniquely identifies the function. The function descriptor contains the address of the function's actual entry point as well as its global data pointer (gp).

**Global data pointer (gp).** The address of a reference location in a load module's data segment, usually kept in a specified general register during execution. Each load module has a single such reference point, typically near the middle of the load module's linkage table. Applications use this pointer as a base register to access linkage table entries, and data that is local to the load module.

**Link time.** The time when a program or DLL is processed by the linker. Any activity taking place at link time is static.

**Linkage table.** A table of addresses that contains pointers to code or data that is external to the load module, or that cannot be addressed directly. Each load module contains a linkage table in its data segment, which allows external references to be bound dynamically without modifying the application's code.

**Load module.** An executable unit produced by the linker, either a main program or a DLL. A program consists of at least a main program, and may also require one or more DLLs to be loaded to satisfy its dependencies.

**Own data.** Data belonging to a load module that is referenced directly from that load module and that is not subject to the binding order. If a module references a data item symbolically, and another module earlier in the binding order defines an item with the same symbolic name, the reference is bound to the data item in the earlier module. If this is the case, the data is not "own." Typically, own data is local in scope.

**PC-relative addressing.** Code that uses its own address (commonly called the program counter, or "PC"; this is called the instruction pointer, or IP, in the IA-64 architecture) as a base register for addressing other code and data.

**Position-independent code (PIC).** This term has a dual meaning. First, position-independent code is designed so that it contains no dependency on its own load address; usually, this is accomplished by using pc-relative addressing so that the code does not contain any absolute addresses. Second, it also implies that the code is also designed for dynamic binding to global data; this is usually done by using indirect addressing through a linkage table.

**Preserved register.** A register that is guaranteed to be preserved across a procedure call.

**Program invocation time.** The time when a program or DLL is loaded into memory in preparation for execution. Activities taking place at program invocation time are generally performed by the system loader or dynamic loader.

**Protection area.** A portion of a segment that shares common access protections.

#### Introduction to the IA-64 Software Conventions and Runtime Architecture Guide

**Region.** The IA-64 architecture divides the address space into four or eight regions. In general, the runtime architecture is independent of which segments are assigned to which region.

**Scratch register.** A register that is not preserved across a procedure call.

**Segment.** An area of memory that has specific attributes, and behaves as a fixed unit at runtime. All items within a segment have a fixed address relationship to one another at execution time, and have a common set of attributes. Items in different segments do not necessarily bear this relationship, and an application may not depend on one. For example, the program text segment is defined to contain the main program code, unwind information, and read-only data. The use of this term is not related to the concept of a segment in the IA-32 architecture, nor is it directly related to the concept of a segment in an object file.

**Static.** (1) Any data or code object that is allocated at a fixed location in memory and whose lifetime is that of the entire process, regardless of its scope; (2) A binding that takes place at link time rather than program invocation or execution time.

# **IA-64 Processor Architecture**

It is assumed that applications conforming to this specification will run in a software environment provided by some operating system, and that additional conventions will be specified as part of the Application Binary Interface (ABI) for that operating system. It is further assumed that the operating system will restrict the application's access to the physical resources of the machine, by limiting the privilege level of the application and by using virtual memory to define the address space available to the application.

The IA-64 Application Developer's Architecture Guide (ADAG) defines the IA-64 application instruction set architecture. Programs intended to execute directly on an IA-64 processor use the instruction set, instruction encodings, and instruction semantics defined in the ADAG. Three points deserve explicit mention:

- A program may assume all documented instructions exist.

- A program may assume all documented instructions work.

- A program may use only the instructions defined by the architecture.

In other words, from a program's perspective, the execution environment provides a complete and working implementation of IA-64.

This does not imply that the underlying implementation provides all instructions in hardware, only that the instructions perform the specified operations and produce the specified results. The software conventions neither place performance constraints on systems nor specify what instructions must be implemented in hardware. A software emulation of the architecture could conform to these conventions.

Some processors might support IA-64 as a subset, providing additional instructions or capabilities. Programs that use those capabilities explicitly do not conform to these conventions. Executing those programs on machines without the additional capabilities results in undefined behavior.

These conventions are intended for application use, and so use only features found in user mode. Applications should assume that they will execute in user mode (privilege level 1, 2, or 3), and that any attempt to use processor resources restricted to privilege level 0 will cause a trap that may terminate the process.

## 2.1 Application State and Programming Model

An application may use all features of IA-64 that are described in the Application State and Programming Model section of the ADAG.

Application use of the break instruction is subject to the following conventions:

• Immediate operands whose three highest-order bits are 000 are reserved for architected software interrupts. These software interrupts are listed in Table 2-1. Application programs (typically language runtime support libraries) may check for these conditions and raise these interrupts, but are not required to do so. Immediate operands in this range, and not listed in the table, are reserved for future use.

- Immediate operands whose three highest-order bits are 001 are available for application use as software interrupts. The behavior of these interrupts, however, is ABI specific.

- Immediate operands whose two highest-order bits are 01 are reserved for debugger breakpoints. Use of debugger breakpoints is ABI specific.

- Immediate operands whose highest-order bit is 1 are reserved for definition by each ABI. It is expected that some operating systems may use values in this range for system-level debugging features and system calls.

**Table 2-1. Software Interrupts**

| Operand | Software Interrupt                                                                                                                         |

|---------|--------------------------------------------------------------------------------------------------------------------------------------------|

| 0       | Unknown program error (typically an indirect branch through an uninitialized pointer, which often leads to a bundle containing all zeroes) |

| 1       | Integer divide by zero                                                                                                                     |

| 2       | Integer overflow                                                                                                                           |

| 3       | Range check/bounds check error                                                                                                             |

| 4       | Nil pointer dereference                                                                                                                    |

| 5       | Misaligned data                                                                                                                            |

| 6       | Decimal overflow                                                                                                                           |

| 7       | Decimal divide by zero                                                                                                                     |

| 8       | Packed decimal error                                                                                                                       |

| 9       | Invalid ASCII digit (unpacked decimal arithmetic)                                                                                          |

| 10      | Invalid decimal digit (packed decimal arithmetic)                                                                                          |

| 11      | Paragraph stack overflow (COBOL)                                                                                                           |

# 2.2 Floating-point Programming Model

An application may use all features of the processor architecture that are described in the Floating-Point Programming Model section of the ADAG.

# intel® Memory Model

These conventions define a virtual memory system with a 64-bit virtual address space per process. Each operating system may divide this address space into different portions, and assign specific uses to each portion.

This chapter describes the types of memory segments and protection areas that an application process uses, and documents the assumptions that an application may make about those segments. From a different perspective, it documents the minimum requirements that must be satisfied by an operating system with respect to its allocation of these program segments in the virtual address space.

The term *segment* is used here to identify an area of memory that has a specific use within an application and has no fixed address relationship to any other segment. Thus, relative distances between any two items belonging to the same segment are constant once the program has been linked, but the distance between two items in different segments is not fixed. It does not imply the use of hardware segmentation, or any specific allocation of segments to hardware regions. In particular, this definition of segment has no relation to the traditional IA-32 segment, nor does it necessarily correspond exactly to the definition of a segment in an object file.

Segments are composed of one or more protection areas. The term *protection area* is used to indicate an area of memory that has common protection attributes.

#### 3.1 **Program segments**

Table 3-1 lists the types of program segments that are defined by the runtime architecture, and defines the minimum set of attributes that an operating system must provide for these segments.

**Table 3-1. Program Segments**

| Segment Type  | Sharable | Quantity          | Address by          | Contents                                         |

|---------------|----------|-------------------|---------------------|--------------------------------------------------|

| Text          | Yes      | 1 per load module | IP or linkage table | Text, unwind information, constants and literals |

| Short Data    | No       | 1 per load module | gp                  | Static data, bss, linkage tables                 |

| Long Data     | No       | any               | linkage table       | Long data, bss                                   |

| Неар          | No       | any               | pointer             | Heap data                                        |

| Stack         | No       | 1 per thread      | sp                  | Memory stacks                                    |

| Backing store | No       | 1 per thread      | bsp                 | Backing store for register stacks                |

| Thread data   | No       | 1 per thread      | tp                  | Thread-local storage                             |

| Shared data   | Yes      | any               | pointer             | Shared memory                                    |

The sharable attribute indicates whether or not the memory contained within such a segment may be shared between two or more processes. For text segments, this implies that an operating system will probably not grant write access, in order to make the text segment pure. For this reason, the runtime architecture does not place anything into the text segment that may need to be written at either program invocation time or execution time.

A program consists of several load modules: the main program, and one for each DLL that it uses. Each load module consists of at least a text segment and a short data segment. The addresses of these segments are not fixed at link time, so all accesses to these segments must be either pcrelative (for text), gp-relative (for short data and the linkage table), or indirect via the linkage table. The gp register and its conventions are described in Chapter 8, "Procedure Linkage".

DLL data may be allocated at execution time. This implies that DLL data segment sizes need not be fixed at linkage time.

Each operating system is expected to provide some form of heap management, although the runtime architecture does not have any explicit dependencies on such. The API for obtaining heap memory, however, is operating system dependent, and the runtime architecture places no restrictions on the locations or contiguity of separately-allocated items from the heap.

Each thread is provided with two stacks: one for the classical memory stack, and one for the register stack backing store. Each thread also has a separate data segment for thread-local storage. These segments must all be allocated from the process' virtual address space, so that one thread may use a pointer that refers to another thread's local storage. The sp register and its conventions are described in Chapter 7, "Memory Stack,", and the bsp register is described in Chapter 6, "Register Stack". The tp register is reserved to provide a handle for accessing thread-local storage, but this usage is ABI dependent.

Like the heap, shared data segments are obtained through an operating system-specific API. The runtime architecture places no restrictions on the locations of these segments.

## 3.2 Protection areas

Table 3-2 lists the minimum access protection for the protection areas defined in the runtime architecture:

**Table 3-2. Protection Areas**

| Segment    | Protection Area | Min. Access |

|------------|-----------------|-------------|

|            | Text            | Х           |

| Text       | Constants       | R           |

|            | Unwind Tables   | R           |

|            | Static Data     | R, W        |

| Short data | Short Bss       | R, W        |

|            | Linkage Tables  | R, W        |

| Long data  | Long Data       | R, W        |

| Long data  | Bss             | R, W        |

| Неар       | Неар            | R, W        |

**Table 3-2. Protection Areas**

| Segment       | Protection Area | Min. Access |

|---------------|-----------------|-------------|

| Stack         | Stack           | R, W        |

| Backing store | Backing store   | R, W        |

| Thread data   | Thread data     | R, W        |

| Shared data   | Shared data     | R, W        |

In order to make the most effective use of the addressing modes available in IA-64, each load module's data is partitioned into one short and some number of long data segments. The short data segment, addressed by the qp register in each load module, contains the following areas:

- A linkage table, containing pointers to imported data symbols and functions, and to data in the text segments and long data segments.

- A short data area, containing small initialized "own" data items.

- A short bss area, containing small uninitialized "own" data items.

The long data segments contain either or both of the following areas:

- A long data area, containing large initialized data items, and initialized non-"own" data items

of any size.

- A long bss area, containing large uninitialized data items, and uninitialized non-"own" data items of any size.

"Own" data items are those that are either local to a load module, or are such that all references to these items from the same load module will always refer to these items. That is, they are not subject to being overridden by an exported symbol of the same name in another load module. All data items in the main program satisfy this definition, since the main program is always the first load module in the binding sequence. Since non-"own" variables cannot be referenced directly, there is no benefit to placing them in the short data or bss area.

Small "own" data items are placed in the short bss or short data, and are guaranteed to be within 2 megabytes, in either direction, of the gp address, so compilers may use a short direct addressing sequence (using the add with 22-bit immediate instruction) to access any data item allocated in these areas. The compiler should place all "own" data items that are 8 bytes or less in size, regardless of structure, in the short data or short bss areas.

All other data items, including items that are larger than 8 bytes in size, or that require indirect addressing because of load-time binding, must be placed in the long data or long bss area. The compiler must address these items indirectly, using a linkage table entry. Linkage table entries are typically allocated by the linker in response to a relocation request generated by the compiler; an entry in the linkage table is either an 8-byte pointer to a data item, or a 16-byte function descriptor. A function descriptor placed in the linkage table is a local copy of an "official" function descriptor that is generally allocated by the linker or dynamic loader.

This design allows for a maximum size of 4 megabytes for the short data segment, since everything must be addressable via the gp register using the 22-bit add immediate instruction. Given that linkage table entries are 8 byte pointers for data references, and 16 bytes long for procedure references, this allows for up to 256,000 individually-named variables and functions. If a load module requires more than this, the compilers will need to support a "huge" memory model, which is not described here.

Protection areas are required to be aligned only as strictly as their contents.

### 3.3 Data Allocation

#### 3.3.1 Global Variables

Common blocks, dynamically allocated regions (for example, from malloc), and external data items greater than 8 bytes must all be aligned on a 16-byte boundary. Smaller data items must be aligned on the next larger power-of-two boundary. Table 3-3 shows the alignment requirements for different size objects.

**Table 3-3. Alignment Requirements for Global Objects**

| Size in bytes | Alignment required       |

|---------------|--------------------------|

| 1             | none                     |

| 2             | 0 mod 2 (even addresses) |

| 3–4           | 0 mod 4                  |

| 5–8           | 0 mod 8                  |

| 9 and up      | 0 mod 16                 |

Access to global variables that are not known (at compile time) to be defined in the same load module must be indirect. Each load module has a linkage table in its data segment, pointed to by the gp register; code must load a pointer to the global variable from the linkage table, then access the global variable through the pointer. Access to globals known to be defined in the same load module or to static locals may be made with a gp-relative offset.

#### 3.3.2 Local Static Data

Access to local static data can be made with a gp-relative offset.

#### 3.3.3 Constants and Literals

Constants and literals may be placed in the text segment or in the data segment. If placed in the text segment, the access must be pc-relative or indirect using a linkage table entry.

Literals placed in the data segment may be placed in the short initialized data area if they are 8 bytes or less in size. Larger literals must be placed in the long initialized data area or in the text segment. Literals in the long initialized data area require an indirect access using a linkage table entry.

## 3.3.4 Local Memory Stack Variables

Access is sp-relative.

Stack frames must always be aligned on a 16-byte boundary. That is, the stack pointer register must always be aligned on a 16-byte boundary.

# Data Representation

Applications running in a 64-bit environment use either the "P64" or "LP64" data model: integers are always 32 bits, while pointers are 64 bits. Long integers may be either 32 or 64 bits, depending on the data model: they are 32 bits in "P64" and 64 bits in "LP64".

Within this specification, the term *halfword* refers to a 16-bit object, the term *word* refers to a 32-bit object, the term *doubleword* refers to a 64-bit object, and the term *quadword* refers to a 128-bit object.

The following sections define the size, alignment requirements, and hardware representation of the standard C and Fortran data types.

Note:

IA-64 hardware/operating system software may have support for misaligned access, with some added performance cost. Some implementations may emulate mis-alignment support by trapping. The alignment rules presented in this section are to help improve performance.

# 4.1 Fundamental Types

Table 4-1 lists the scalar data types supported by the architecture. Sizes and alignments are shown in bytes. A null pointer (for all types) has the value zero.

Table 4-1. Scalar Data types Supported by IA-64

| Туре     | С                                                | Size | Align | Hardware Representation  |

|----------|--------------------------------------------------|------|-------|--------------------------|

|          | char<br>signed char                              | 1    | 1     | signed byte              |

|          | unsigned char                                    | 1    | 1     | unsigned byte            |

|          | short<br>signed short                            | 2    | 2     | signed halfword          |

|          | unsigned short                                   | 2    | 2     | unsigned halfword        |

| Integral | int<br>signed int<br>enum                        | 4    | 4     | signed word              |

|          | unsigned int                                     | 4    | 4     | unsigned word            |

|          | int64<br>signedint64                             | 8    | 8     | signed doubleword        |

|          | unsignedint64                                    | 8    | 8     | unsigned doubleword      |

|          | int128 <sup>1</sup><br>signedint128 <sup>1</sup> | 16   | 16    | signed 128-bit integer   |

|          | unsignedint128 1                                 | 16   | 16    | unsigned 128-bit integer |

| Pointer  | any-type * any-type (*) ()                       | 8    | 8     | unsigned doubleword      |

Table 4-1. Scalar Data types Supported by IA-64

| Туре           | С                     | Size | Align | Hardware Representation        |

|----------------|-----------------------|------|-------|--------------------------------|

|                | float                 | 4    | 4     | IEEE single precision          |

|                | double                | 8    | 8     | IEEE double precision          |

| Floating-point | float80 <sup>2</sup>  | 16   | 16    | IEEE double-extended precision |

|                | float128 <sup>3</sup> | 16   | 16    | quad precision                 |

#### NOTES:

- 1. \_\_int128 is not directly supported by the hardware, and these conventions do not require an operating system environment to support this type through emulation. Size and alignment conventions are specified here, however, for those implementations that do choose to support this type. Note also that the (non-standard) long long data type is not specified by these conventions, and may be implemented as a 64-bit integer, a 128-bit integer, or not at all.

- 2. \_\_float80 is the IA-64 extended 80-bit quantity, but the software standard is to treat it as a 16-byte quantity. It is referenced using ldfe and stfe instructions. This type has the same precision and range as the 80 bit extended data type of the IA-32 architecture, but with different size and alignment.

- 3. \_\_float128 is not directly supported by the hardware, and these conventions do not require an operating system environment to support this type through emulation. Size, representation, and alignment conventions are specified here, however, for those implementations that do choose to support this type. A quad-precision floating-point number is a 128-bit quantity with a sign bit, a 15-bit biased exponent, and a 112-bit mantissa with an implicit integer bit.

# 4.2 Aggregate Types

Aggregates (structures and arrays) and unions assume the alignment of their most strictly aligned component. The size of any object, including aggregates and unions, is always a multiple of the object's alignment. An array uses the same alignment as its elements. Structure and union objects can require padding to meet size and alignment constraints. The contents of any padding is undefined.

- An entire structure or union object is aligned on the same boundary as its most strictly aligned member.

- Each member is assigned to the lowest available offset with the appropriate alignment. This may require *internal padding*, depending on the previous member.

- A structure's size is increased, if necessary, to make it a multiple of the alignment. This may require *tail padding*, depending on the last member.

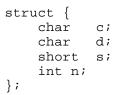

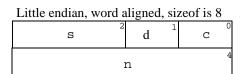

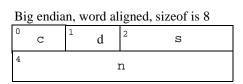

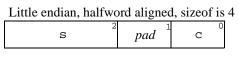

In the following figures, members' byte offsets appear in the upper right corners for little-endian, in the upper left for big-endian.

Figure 4-1. Structure Smaller Than a Word

Figure 4-2. No Padding

```

struct {

char c;

short s;

};

```

Figure 4-3. Internal Padding

Little endian, doubleword aligned, sizeof is 24

| pad    | 1 0<br>C |

|--------|----------|

| po     | ad 4     |

| d (le  | ow) 8    |

| d (hi  | igh) 12  |

| pad 18 | 16<br>S  |

| pe     | ad 20    |

struct {

char c;

double d;

short s;

};

Big endian, doubleword aligned, sizeof is 24

| 0  | С        | pad pad |        |  |  |

|----|----------|---------|--------|--|--|

| 4  |          |         | pad    |  |  |

| 8  | d (high) |         |        |  |  |

| 12 | d (low)  |         |        |  |  |

| 16 |          | s       | 18 pad |  |  |

| 20 | pad      |         |        |  |  |

Figure 4-4. Internal and Tail Padding

```

union {

char c;

short s;

int j;

};

```

Little endian, word aligned, sizeof is 4

| pad   | 1 | C |

|-------|---|---|

| pad 2 | S | 0 |

|       | j | 0 |

Big endian, word aligned, sizeof is 4

| Dig Ciluia | ii, word air | igned, sizeor is + |  |  |  |

|------------|--------------|--------------------|--|--|--|

| C          | 1            | pad                |  |  |  |

| 0          | S            | <sup>2</sup> pad   |  |  |  |

| 0          |              | j                  |  |  |  |

Figure 4-5. Union Allocation

## 4.3 Bit Fields

C struct and union definitions may have *bit-fields* that define integral objects with a specified number of bits. Table 4-2 defines the allowable widths and corresponding range of values for bit fields of each base type.

Table 4-2. Bit Field Base Types

| Base Type      | Width w | Range                     |

|----------------|---------|---------------------------|

| unsigned char  | 1 to 8  | 0 to 2 <sup>w</sup> -1    |

| signed char    | 1 to 8  | $-2^{W-1}$ to $2^{W-1}-1$ |

| unsigned short | 1 to 16 | 0 to 2 <sup>w</sup> -1    |

| signed short   | 1 to 16 | $-2^{w-1}$ to $2^{w-1}-1$ |

| unsigned int   | 1 to 32 | 0 to 2 <sup>w</sup> -1    |

| signed int     | 1 to 32 | $-2^{W-1}$ to $2^{W-1}-1$ |

| unsigned long  | 1 to 64 | 0 to 2 <sup>w</sup> -1    |

| signed long    | 1 to 64 | $-2^{w-1}$ to $2^{w-1}-1$ |

Bit-fields obey the same size and alignment rules as other structure and union members, with the following additions:

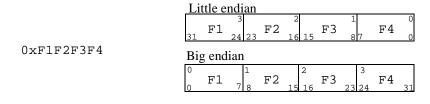

Bit-fields are allocated from right to left (least to most significant) for little endian. They are allocated left to right (most to least significant) for big-endian.

A bit-field must entirely reside in a storage unit appropriate for its declared type. For example, a bit field of type short must never cross a halfword boundary.

Bit-fields may share a storage unit with other struct/union members, including members that are not bit-fields. Of course, each struct member occupies a different part of the storage unit.

• Unnamed bit-fields' types do not affect the alignment of a structure or union. Zero-length unnamed bit-fields force the alignment of subsequent members to the boundary corresponding to the size of the unnamed bit-field.

The following figures show struct and union member byte offsets in the upper corners; bit numbers appear in the lower corners.

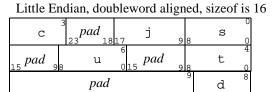

Figure 4-6. Bit Numbering

```

struct {

int    j:5;

int    k:6;

int    m:7;

};

```

Figure 4-7. Bit Field Allocation

```

struct {

short s:9;

__int64 j:9;

char c;

short t:9;

short u:9;

char d;

};

```

pad

Figure 4-8. Boundary Alignment

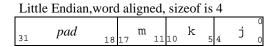

```

struct {

char c;

short s:8;

};

```

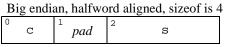

#### Little-endian, halfword aligned, sizeof is 2

|    |   | 1 |   | ( |

|----|---|---|---|---|

|    | S |   | C |   |

| 15 |   | 8 |   |   |

#### Big-endian, halfword aligned, sizeof is 2

| 0 |   | 1 |   |    |

|---|---|---|---|----|

|   | С | 0 | s | 16 |

|   |   | 8 |   | 1. |

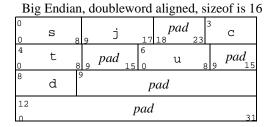

Figure 4-9. Storage Unit Sharing

```

union {

char c;

short s:8;

};

```

#### Little-endian, halfword aligned, sizeof is 2

|    | pad | 1 |   | С | 0 |

|----|-----|---|---|---|---|

|    | pad |   |   | s | 0 |

| 15 | •   | 8 | 7 |   | 0 |

#### Big-endian, halfword aligned, sizeof is 2

| 0 | С |   | 1 | pad |    |

|---|---|---|---|-----|----|

| 0 | s | 7 | 8 | pad | 15 |

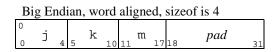

Figure 4-10. Union Allocation

```

struct {

char    c;

int    :0;

char    d;

short   :9;

char    e;

char    :0;

};

```

Little-endian, byte aligned, sizeof is 9

|    |     |    | :0 |   | 1     | С | 0 |

|----|-----|----|----|---|-------|---|---|

| 15 | pad | 98 | :9 | 6 | pad 5 | d | 4 |

|    |     |    |    |   | ,     | е | 8 |

#### Big-endian, byte aligned, sizeof is 9

| 0 | С | 1 |     |        | :0 |    |     |    |

|---|---|---|-----|--------|----|----|-----|----|

| 4 | d | 5 | pad | 6<br>0 | :9 | 89 | pad | 15 |

| 8 | е |   |     |        |    |    |     |    |

Figure 4-11. Unnamed Bit Fields

Note that unnamed bit fields do not affect the alignment of the structure.

As the examples show, int and \_\_int64 bit-fields (including signed and unsigned) usually pack more densely than smaller base types. One can use char and short bit-fields to force allocation within those types, but int is generally more efficient.

# 4.4 Fortran Data Types

Table 4-3 shows the correspondence between ANSI Fortran's scalar types and the processor's data types. ANSI Fortran requires REAL and INTEGER to be the same size. Many Fortran compilers allow INTEGER\*n, LOGICAL\*n, and REAL\*n to specify specific processor sizes. ("n" is in bytes). The COMPLEX data type is treated exactly the same as a C structure composed of two float members.

**Table 4-3. Fortran Data Types**

| Туре           | Fortran             | Size | Align<br>(bytes) | Hardware Representation |

|----------------|---------------------|------|------------------|-------------------------|

| Character      | aracter CHARACTER*n |      | 1                | byte                    |

| Integral       | LOGICAL             | 4    | 4                | word                    |

| integral       | INTEGER             | 4    | 4                | signed word             |

|                | REAL                | 4    | 4                | IEEE single-precision   |

| Floating-point | DOUBLE PRECISION    | 8    | 8                | IEEE double-precision   |

|                | COMPLEX             | 8    | 4                | 2 IEEE single-precision |

# Register Usage

# 5.1 Partitioning

Registers are partitioned into the following classes:

- **Scratch** registers may be modified by a procedure call; the caller must save these registers before a call if needed ("caller save").

- **Preserved** registers must not be modified by a procedure call; the callee must save and restore these registers if used ("callee-save").

- Automatic registers are saved and restored automatically by the call/return mechanism.

- **Constant** or **Read-only** registers contain a fixed value that cannot be changed by the program.

- **Special** registers are used in the call/return mechanism. The conventions for these registers are described individually below.

# 5.2 General Registers

General registers are used for integer arithmetic and other general-purpose computations. Table 5-1 lists the general registers.

| <b>Table</b> | <b>5-1.</b> | General | l Reg | isters |

|--------------|-------------|---------|-------|--------|

|--------------|-------------|---------|-------|--------|

| Register   | Class     | Usage                                |

|------------|-----------|--------------------------------------|

| r0         | constant  | Always 0                             |

| r1         | special   | Global data pointer (gp)             |

| r2-r3      | scratch   | Use with 22-bit immediate add        |

| r4–r7      | preserved |                                      |

| r8–11      | scratch   | Procedure return value               |

| r12        | special   | Memory stack pointer (sp)            |

| r13        | special   | Reserved as a thread pointer (tp)    |

| r14–r31    | scratch   |                                      |

| in0-in95   | automatic | Stacked input registers (see below)  |

| loc0-loc95 | automatic | Stacked local registers (see below)  |

| out0-out95 | scratch   | Stacked output registers (see below) |

- **r1** is the global data pointer (gp), which is designated to hold the address of the currently addressable global data segment. Its use is subject to the following conventions:

- **a.** On entry to a procedure, gp is guaranteed valid for that procedure.

- **b.** At any direct procedure call, gp must be valid (for the caller). This guarantees that an import stub (see Section 8.4.1) can access the linkage table.

- **c.** Any procedure call (indirect or direct) may modify gp—unless the call is known to be local to the load module.

- **d.** At procedure return, gp must be valid (for the returning procedure). This allows the compiler to optimize calls known to be local (i.e., the exceptions to Rule 'c').

The effect of these rules is that gp must be treated as a scratch register at a point of call (i.e., it must be saved by the caller), and it must be preserved from entry to exit.

- **r4-r7** are general-purpose preserved registers, and can be used for any value that needs to be preserved across a procedure call. A procedure using one of the preserved general registers must save and restore the caller's original contents, including the NaT bits associated with the registers, without generating a NaT consumption fault. This can be done by either copying the register to a stacked register or by using the st8.spill and ld8.fill instructions and then saving ar.unat.

- **r8** is used as the struct/union return pointer register. If the function being called returns a struct or union value larger than 32 bytes, then register GR 8 contains, on entry, the appropriately-aligned address of the caller-allocated area to contain the value being returned. (See Section 8.6.)

- **r8–r11** are used for non-floating-point return values up to 32 bytes. Functions do not have to preserve their values for the caller.

- **r12** is the *stack pointer*, which holds the limit of the current stack frame, the address of the stack's bottom-most valid word. At all times, the stack pointer must point to a 0 mod 16 aligned area. The stack pointer is also used to access any memory arguments upon entry to a function. Except in the case of dynamic stack allocation (e.g., alloca), this register is preserved across any functions called by the current function. A call to a function that does not preserve the stack pointer must notify the compiler, to cause the generation of code that behaves properly. Failure to notify the compiler leads to undefined behavior. The standard function calling sequence does not include any method to detect such failures. This allows the compiler to use the stack pointer to reference stack items without having to set up a frame pointer for this purpose.

- **r13** is reserved for use as a *thread pointer*. The usage of this register is ABI specific. Programs conforming to these conventions may not modify this register.

- r32–r39 (in0–in7) are used as incoming argument registers. Arguments beyond these registers appear in memory, as explained in Chapter 8. Refer to the discussion below on structures and unions.

- r32-r127 are stacked registers. Code may allocate a register stack frame of up to 96 registers with the alloc instruction, and partition this frame into three regions: input registers (in0, in1, ...), local registers (loc0, loc1, ...), and output registers (out0, out1, ...). The input and local regions are automatic, and the output region is scratch. See Chapter 6, "Register Stack" for more information.

# 5.3 Floating-point Registers

Floating-point registers are used for floating-point computations and certain integer computations, such as multiply and divide. Table 5-2 lists the floating-point registers.

**Table 5-2. Floating-Point Registers**

| Register | Class     | Usage                         |

|----------|-----------|-------------------------------|

| f0       | constant  | Always 0.0                    |

| f1       | constant  | Always 1.0                    |

| f2-f5    | preserved |                               |

| f6-f7    | scratch   |                               |

| f8–f15   | scratch   | Argument/return registers     |

| f16–f31  | preserved |                               |

| f32–f127 | scratch   | Rotating registers or scratch |

- **f2–f5** and **f16–f31** are preserved floating-point registers, and can be used for any value that needs to be preserved across a procedure call. A procedure using one of the preserved floating-point registers must save and restore the caller's original contents without generating a NaT consumption fault. This can be done by using the stf.spill and ldf.fill instructions.

- **f8–f15** are used as incoming floating-point argument registers. Floating-point arguments are placed in these registers when possible. Arguments beyond the registers appear in memory, as explained in Section 8.5. Within the called function, these are local scratch registers and are not preserved for the caller.

- Floating-point return values also appear in these registers. Single, double, and extended values are all returned using the appropriate format.

- **f32–f127** can be used as rotating registers. They are available as normal scratch registers if rotation is not being used.

# 5.4 Predicate Registers

Predicate registers are single-bit-wide registers used for controlling the execution of predicated instructions. Table 5-3 lists the predicate registers.

**Table 5-3. Predicate Registers**

| Register | Class     | Usage    |

|----------|-----------|----------|

| p0       | constant  | always 1 |

| p1-p5    | preserved | fixed    |

| p6-p15   | scratch   | fixed    |

| p16-p63  | preserved | rotating |

# 5.5 Branch Registers

Branch registers are used for making indirect branches. Table 5-4 lists the branch registers.

Table 5-4. Branch Registers

| Register | Class     | Usage       |

|----------|-----------|-------------|

| b0       | scratch   | Return link |

| b1-b5    | preserved |             |

| b6-b7    | scratch   |             |

• **b0** contains the return address on entry to a procedure; it is a scratch register otherwise.

# 5.6 Application Registers

Application registers are special-purpose registers designated for application use. Table 5-5 lists the application registers.

**Table 5-5. Application Registers**

| Register    | Class     | Usage                                 |

|-------------|-----------|---------------------------------------|

| ar.fpsr     | see below | Floating-point status register        |

| ar.rnat     | automatic | RSE NaT collection register           |

| ar.unat     | preserved | User NaT collection register          |

| ar.pfs      | special   | Previous function state               |

| ar.bsp      | read-only | Backing store pointer                 |

| ar.bspstore | special   | Backing store store pointer           |

| ar.rsc      | see below | RSE control                           |

| ar.lc       | preserved | Loop counter                          |

| ar.ec       | automatic | Epilog counter (preserved in ar.pfs)  |

| ar.ccv      | scratch   | Compare and Exchange comparison value |

| ar.itc      | read-only | Interval time counter                 |

| ar.k0-ar.k7 | read-only | Kernel registers                      |

• **ar.fpsr** is the floating-point status register. This register is divided into several fields: **Trap Disable Bits (bits 5–0).** The trap disable bits must be preserved by the callee, except for procedures whose documented purpose is to change these bits.

**Status Field 0.** The control bits must be preserved by the callee; except for procedures whose documented purpose is to change these bits. The flag bits are the IEEE floating point standard sticky bits and are part of the static state of the machine.

**Status Field 1.** This status field is dedicated for use by divide and square root code, and must always be set to standard values at any procedure call boundary (including entry to exception handlers). These standard values are: trap disable set, round-to-nearest mode, 80-bit (extended) precision, widest range for exponent on, and flush-to-zero mode off. The flag bits are scratch.

**Status Fields 2 and 3.** The control bits in these status fields must agree with the control bits in status field 0, and the trap disable bits should always be set at procedure calls and returns. The flag bits are always available for scratch use.

- **ar.rnat** holds the NaT bits for values stored by the register stack engine. These bits are saved automatically in the register stack backing store.

- **ar.unat** holds the NaT bits for values stored by the st8.spill instruction. As a preserved register, it must be saved before a procedure can issue any st8.spill instructions. The saved copy of ar.unat in a procedure's frame hold the NaT bits from the registers spilled by its caller; these NaT bits are thus associated with values local to the caller's caller.

- **ar.pfs** contains information that records the state of the caller's register stack frame and epilog counter. It is overwritten on a procedure call; therefore, it must be saved before issuing any procedure calls, and restored prior to returning.

- **ar.bsp** contains the address in the backing store corresponding to the base of the current frame. This register may be modified only as a side effect of writing ar.bspstore while the Register Stack Engine (RSE) is in enforced lazy mode.

- **ar.bspstore** contains the address of the next RSE store operation. It may be read or written only while the RSE is in enforced lazy mode. Under normal operation, this register is managed by the RSE, and application code should not write to it, except when performing a stack switching operation.

- **ar.rsc** is the register stack configuration register. This register is divided into several fields: **Mode.** This field controls the RSE behavior, and has scratch behavior. On a return, this field may be set to a standard value.

**Privilege level.** This field controls the privilege level at which the RSE operates, and may not be changed by non-privileged software.

**Endian mode.** This field controls the byte ordering used by the RSE, and should not be changed by an application.

**Load distance.** This field is used by a RSE control instruction, and has scratch behavior.

# intel<sub>®</sub> Register Stack

General registers 32 through 127 form a register stack that is automatically managed across procedure calls and returns. Each procedure frame on the register stack is divided into two dynamically-sized regions—one for input parameters and local variables, and one for output parameters. On a procedure call, the registers are automatically renamed by the hardware so that the caller's output registers form the base of the callee's new register stack frame. On return, the registers are restored to the previous state, so that the input and local registers are preserved across the call.

The alloc instruction is used at the beginning of a procedure to allocate the input, local, and output regions; the sizes of these regions are supplied as immediate operands. A procedure is not required to issue an alloc instruction if it does not need to store any values in its register stack frame. It may still read values from input registers, but it may not write to a stack register without first issuing an alloc instruction.

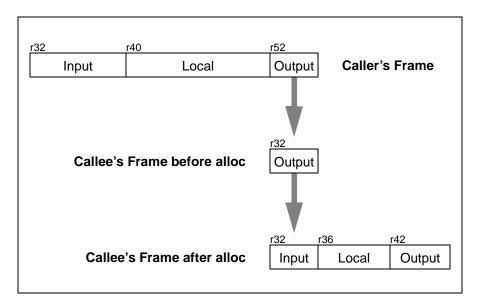

Figure 6-1 illustrates the operation of the register stack across an example procedure call. In this example, the caller allocates eight input, twelve local, and four output registers, and the callee allocates four input, six local, and five output registers.

The actual registers to which the stacking registers are physically mapped are not directly addressable by the application software.

#### 6.1 Input and Local Registers

The hardware makes no distinction between input and local registers. The caller's output registers automatically become the callee's entire register stack frame on a procedure call, with all registers initially allocated as output registers. An alloc instruction may increase or decrease the total size of the register stack frame, and may adjust the boundary between the input and local region and the output region.

The software conventions specify that up to eight registers are used for parameter passing. Any registers in the input and local region beyond those eight may be allocated for use as preserved locals. Floating-point parameters may produce "holes" in the parameter list that is passed in the general registers; those unused input registers may also be used for preserved locals.

The caller's output registers do not need to be preserved for the caller. Once an input parameter is no longer needed, or has been copied elsewhere, that register may be reused for any other purpose within the procedure.

#### 6.2 **Output Registers**

Up to eight output registers are used for passing parameters. If a procedure call requires fewer than eight general registers for its parameters, the calling procedure does not need to allocate more than are needed. If the called procedure expects more parameters, it will allocate extra input registers; these registers will be uninitialized.

Figure 6-1. Operation of the Register Stack

A procedure may also allocate more than eight registers in the output region. While the extra registers may not be used for passing parameters, they can be used as extra scratch registers. On a procedure call, they will show up in the called procedure's output area as excess registers, and may be modified by that procedure. The called procedure may also allocate few enough total registers in its stack frame that the top of the called procedure's frame is lower than the caller's top of frame, but those registers will become available again when control returns to the caller.

# 6.3 Rotating Registers

A subset of the registers in the procedure frame may be designated as rotating registers. The rotating register region always starts with r32, and may be any multiple of eight registers in number, up to a maximum of 96 rotating registers. The renaming is under control of the Rotating Register Base (RRB).

If the rotating registers include any or all of the output registers, software must be careful when using the output registers for passing parameters, since a non-zero RRB will change the virtual register numbers that are part of the output region. In general, software should either ensure that the rotating region does not overlap the output region, or that the RRB is cleared to zero before setting output parameter registers.

## 6.4 Frame Markers

The current application-visible state of the stack frame is stored in an architecturally inaccessible register called the current frame marker. On a procedure call, this register is automatically saved by copying it to an application register, the previous function state (ar.pfs). The current frame marker is modified to describe a new stack frame whose input and local area is initially zero size, and

whose output area is equal in size to the previous output area. On return, the previous frame state register is used to restore the current frame marker to its earlier value, and the base of the register stack is adjusted accordingly.

It is the responsibility of a procedure to save the previous function state register before issuing any procedure calls of its own, and to restore it before returning.

# 6.5 Backing Store for Register Stack

When the depth of the procedure call stack exceeds the capacity of the physical register file, the hardware frees physical registers by saving them into a memory stack. This backing store is distinct from the memory stack described in the next chapter.

As returns unwind the procedure call stack, the hardware also restores previously-saved physical registers from the backing store.

The operation of this register stack engine (RSE) is mostly transparent to application software. While the RSE is running, application software may not examine the contents of the backing store, and may not make any assumptions about how much of the register stack is still in physical registers or in the backing store. In order to examine previous stack frames, application software must synchronize the RSE with the flushrs instruction. Synchronizing the RSE forces all stack frames up to, but not including, the current frame to be saved in backing store, allowing the software to examine the contents of the backing store without asynchronous operations modifying the memory. Modifications to the backing store require setting the RSE to "enforced lazy mode" after synchronizing it, which prevents the RSE from doing any operations other than those required by calls and returns. The procedure for synchronizing the RSE and setting the mode is described in Section 10.2, "User-level thread switch, coroutines" on page 10-2.

The backing store grows towards higher addresses. When the RSE is synchronized and in enforced lazy mode, the top of the stack corresponding to the top of the previous procedure frame is available in the Backing Store Pointer (bsp) application register.

Even when the RSE is in enforced lazy mode, the bsp must always point to a valid backing store address, since the operating system may need to start the RSE to process an exception.

A NaT collection register is stored into the backing store after each group of 63 physical registers. For each register stored, its NaT bit is shifted into the collection register. When the bsp reaches the doubleword just before a 64 doubleword boundary, the RSE stores the collection register. Software can determine the position of the NaT collection registers in the backing store by examining the memory address. This process is described in greater detail in the ADAG.

# intel<sub>®</sub> *Memory Stack*

The memory stack is used for local dynamic storage, spilled registers, and parameter passing. It is organized as a stack of *procedure frames*, beginning with the main program's frame at the base of the stack, and continuing towards the top of the stack with nested procedure calls. At the top of the stack is the frame for the currently active procedure. (There may be some system-dependent frames at the base of the stack, prior to the main program's frame, but an application program may not make any assumptions about them.)

The memory stack begins at an address determined by the operating system, and grows towards lower addresses in memory. The stack pointer register, sp, always points to the lowest address in the current, top-most, frame on the stack.

Each procedure creates its frame on entry by subtracting its frame size from the stack pointer, and removes its frame from the stack on exit by restoring the previous value of sp (usually by adding its frame size, but a procedure may save the original value of sp when its frame size may vary).

Because the register stack is also used for the same purposes, not all procedures will need a stack frame. Every non-leaf procedure, however, needs to save at least its return link and the previous frame marker either on the register stack or in the memory stack, so there is an activation record for every non-leaf procedure on one or both of the stacks.

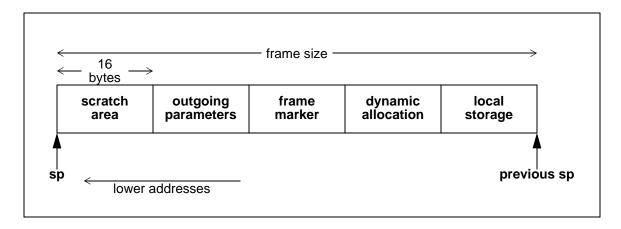

### 7.1 **Procedure Frames**

A procedure frame consists of five regions, as illustrated in Figure 7-1.

Figure 7-1. Procedure frame

These regions are:

Local storage. A procedure may store local variables, temporaries, and spilled registers in this region.